文 / 圖◎ B97/R01周東陞系友

「隨著人工智慧(AI)和高性能運算(HPC)處理器需求升高,台積電 CoWoS 產能過去一直供不應求。在上週歐洲技術研討會,台積電宣布計劃以年均複合成長率(CAGR)超過 60%,持續擴大 CoWoS 產能至 2026 年。因此到 2026 年底,台積電 CoWoS 產能將比 2023 年的水準增加四倍以上。」--<現有CoWoS產能難滿足將來需求!台積電力拚2026前「每年擴大60%」>摘錄自2024年5月24日之財訊雜誌。

2016年底應莊嘉揚教授的邀約寫了一篇關於台積研替生活的專欄,當時最夯的題材是甫推出的InFO封裝技術,主要應用在智慧型手機的AP晶片封裝,搭配當時最先進的10奈米製程。時隔8年,智慧型手機發展日趨飽和,先進製程的微縮逐漸從奈米走向哀米,戰場也逐漸轉向由AI和HPC主導的世界。

就在前一年,2023年初由NV執行長黃仁勳才宣布,搭著ChatGPT的狂潮,AI正迎來他的iphone時刻!眼下所有最熱門的題目幾乎都與AI有關,AI正在大幅地改變我們生活的樣貌,而這一切的根源與大型語言模型(Large Language Model, LLM)與生成式AI (Generative AI)有著密切的關連,而訓練LLM需要非常非常大量的計算資源,這時候由NV和AMD所提供的AI伺服器完全命中這樣的特性!為了因應這樣高運算需求的GPU以及CPU,除了必須用上最先進的二維微縮技術外,GPU/CPU與高頻寬記憶體(High Bandwidth Memory, HBM)之間的異質整合(Heterogeneous Integration)也變得更為關鍵。

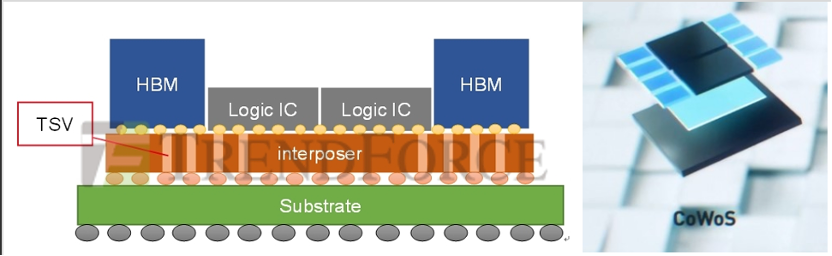

台積電的CoWoS(Chip on Wafer on Substrate)封裝提供了非常好的GPU/CPU與HBM溝通的橋樑,何謂CoWoS呢?他基本上可以拆成「CoW」與「WoS」兩個部分。CoW指的是將晶片(Chip)與Wafer做垂直堆疊,而WoS則是Wafer與基板(Substrate)做堆疊。這樣的好處是能夠利用Wafer (實際上為矽中介層Si interposer)高I/O、細線寬的特性,縮短晶片與晶片之間溝通的距離,降低晶片的延遲特性,此外也能縮減封裝體積、降低功耗等好處,實現所謂的2.5D封裝。

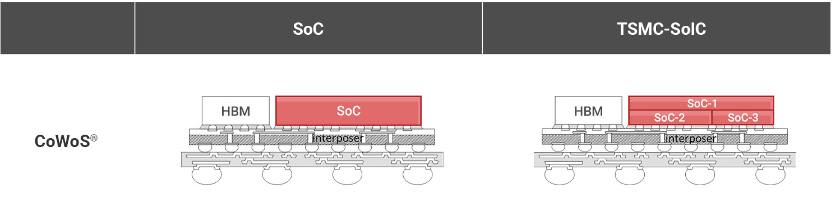

廣為人知的摩爾定律隨著製程微縮至3奈米以下,慢慢逼近了物理的極限,而台積的高層早在10多年前就意識到了這一點,為了解決這個問題,必須依靠所謂的先進封裝來解決,來因應客戶對於晶片效能日益嚴苛的需求。前文提到的InFO、CoWoS都是屬於台積先進封裝的一支,前者主攻消費型電子,主打輕薄及CP值為主;而後者主打的是高效能、高算力的伺服器晶片。而另一個尚未被提及的是叫做SoIC(System on IC)的封裝技術,為業界第一個高密度3D小晶片堆疊技術。他利用晶片對晶片的直接接合技術,不額外透過凸塊做鍵結,實現上下晶片的TSV (Through Silicon Via)直接對接,可大幅提升晶片的I/O數增加晶片算力。SoIC厲害之處是可以與前述的InFO及CoWoS技術做整合,真正達到1+1>2的效果。

隨著先進封裝的發展跟著壯大的還有所謂的小晶片(Chiplet)技術,為什麼需要Chiplet呢?因為隨著2D製程的微縮,晶片的良率變成一個巨大的挑戰,透過小晶片的應用,原本多功能的晶片將細拆成更多不同單一功能的小晶片,再透過先進封裝技術將KGD(known good die)整合進同一顆晶片內,達成良率的提升,除此之外也能讓晶片設計上有更大的彈性、更簡化。以高算力需求的AI晶片為例,在2D微縮製程無法再更細的情況下,只能透過放大光罩尺寸(reticle size)的方式來增加電晶體數目,當晶片的尺寸超過光罩的尺寸時,就很難用原本的方式製造了,這時候chiplet變成了最佳解方,目前AMD的MI300 APU (CPU+GPU)、Apple的M1、M2系列、NVIDIA的Blackwell,都是用這樣的方式。

以上大概簡略的介紹了當前先進封裝的樣貌及趨勢,身為一名先進封裝的模組研發工程師,我們平常的工作就是和整合工程師一同開發下一世代的封裝技術,解決良率及量產的問題,並完成客戶的驗證批(qual lot)驗證。模組工程師必須對所屬的站點有非常高的掌握度,舉凡機台特性、藥水特性以及與前後站的交互作用都必須有一定程度的了解。部門老闆時常勉勵我們要保持好奇心,對於任何看似微小的異狀都必須去問「為什麼?」如此才有可能找到問題的癥結點,進而改善問題、避免問題。

感謝過去在機械系6年扎實的訓練,幫助我們在與廠商開發機台與藥水時能夠有足夠的基礎知識以及對於解方的敏感度,以我負責的電鍍站點為例,我們常常需要考量到機台內的流場、電場及質傳效率對於電鍍表現的影響。而對於機台零組件的耐用程度,抑或是晶片內線路的應力分布及熱傳效應,過去機械系的基礎必修都能夠確實地幫助到我們。先進封裝最常面臨到的問題,正是異質晶片間彼此不同的熱膨脹係數,若晶片間或是線路及高分子材料彼此間的熱膨脹表現不一,會造成晶片的翹曲(warpage)行為嚴重,輕則造成良率下降,重則造成wafer破片造成機台損壞,不可不慎!

隨著AI的興起,客戶對於新技術以及產能的渴求程度日益增加,台積電對於開發期程的要求也是與日俱增。很感謝公司提供了許多Machine learning及JMP統計軟體的教育課程,讓我們在解issue時能有更強大的工具!以我負責的專案為例,面對客戶千奇百怪的設計,我們以往總是得花費許多的時間進行試誤的過程,一次又一次的NTO才能把最佳解BKM找出來;現在透過Machine learning及JMP,我們可以有系統的建立一套預測的model來針對客戶的設計進行分析,進而在更短的時間內給出recipe BKM趕上驗證期程,不僅縮短了開發的時間,也讓我們對於面對的系統有更深刻的認識,我覺得這是在這個AI浪潮下讓我感受最深刻的地方,也是工作上最大的快樂!

台積電緊湊的生活步調,紓壓也成了一個重要的環節。早年學生時期總是在管樂團與棒球隊之間走跳的我,工作之後時間變得比較沒那麼彈性,轉而發展個人就能進行的運動為主,單車運動正是我近期最佳的寫照。一開始是為了求婚,想說利用騎單車減肥,從原本將近80公斤透過一年左右的訓練,體重成功瘦到65公斤,不僅成功娶得美嬌娘,更結交到一群熱愛單車活動的好車友,時常利用周末時間騎遍台灣各大山頭。

在台灣單車圈中,武嶺的完賽時間變成了一個車友之間評斷一個人功力的客觀標準,為此,我積極地透過科學化訓練,透過直驅式訓練台與線上騎乘軟體,努力完成課表,期待以更高的效率獲得騎乘功率的提升。目前我的西進武嶺紀錄停留在3小時32分左右,但隨著寶貝女兒的出生,要如何把工作、家庭以及訓練整合在一起,變成我更重要的課題,時至今日我都還在尋找這個問題最佳解,我想只能透過更多的溝通、協調與妥協,才能夠完成這難度更高的「異質整合」吧!

作者簡介:

2012畢業於台大機械系。2014年畢業於台大機械所固力組,指導教授為莊嘉揚教授,主要研究噴射式大氣電漿鍍膜。隨後進入台積電先進封裝部門,專攻薄膜製程研發迄今。

█ 與家人遊沖繩

█ 2023年96聯賽武嶺盃

█ 台積CoWoS封裝 (來源:台積電)

█ CoWoS結合SoIC (來源:台積電)

█ 引薦實驗室學弟加入台積封裝成功有老師的見證(作者為右一)